The design of Analog and Mixed-Signal (AMS) integrated circuits (ICs) often involves significant manual effort, especially during the transistor sizing process. While Machine Learning techniques in Electronic Design Automation (EDA) have shown promise in reducing complexity and minimizing human intervention, they still face challenges such as numerous iterations and a lack of knowledge about AMS circuit design. Recently, Large Language Models (LLMs) have demonstrated significant potential across various fields, showing a certain level of knowledge in circuit design and indicating their potential to automate the transistor sizing process. In this work, we propose an LLM-based AI agent for AMS circuit design to assist in the sizing process.

The complexity of laboratory environments requires solutions that simplify instrument interaction and enhance measurement automation. Traditional tools often require configuration, software, and programming skills, creating barriers to productivity. Previous approaches, including dedicated software suites and custom scripts, frequently fall short in providing user-friendly solutions that align with programming practices. We present LABIIUM, an AI-enhanced, zero-configuration measurement automation system designed to streamline experimental workflows and improve user productivity.

EEcircuit is an open-source browser-based simulation tool, created Created by Dr Danial Chitnis of Electronics and Electrical Engineering at The University of Edinburgh, for electrical and electronic circuit analysis. EEcircuit’s input is a SPICE compatible netlist, and the output is a plot of current and voltage nodes, information on the simulation results, and a downloadable CSV file for further analysis in external popular analysis software packages such as Numpy and Python. Since the input netlist is text-based, it has the advantage of version control via GitHub, easy sharing, scripting, and automation. The backend of EEcircuit is based on ngspice, and all the computation happens inside the browser using WebAssembly (WASM) technology. Additionally, it respects the user privacy since no data leaves the browser’s sandboxed environment. EEcircuit offers a convenient tool for brainstorming and sharing of circuit simulation with a modern UX/UI contributing to the growing community of the open-source integrated circuit hardware.

Time-to-Digital Converters (TDCs) are major components for the measurements of time intervals. Recent developments in Field-Programmable Gate Array (FPGA) have enabled the opportunity to implement high-performance TDCs, which were only possible using dedicated hardware. In order to eliminate empty histogram bins and achieve a higher level of linearity, FPGA-based TDCs typically apply compensation methods either using multiple delay lines consuming more resources or post-processing, leading to a permanent loss of temporal information. We propose a novel TDC with a single delay line and without compensation to realize a highly linear TDC by encoding the states of the delay lines instead of the thermometer code used in the conventional TDCs.

A multi-line high-performance 2D plotting library using native WebGL. It has a simple and efficient native WebGL line drawing with High update rate which matches the screen's refresh rate (FPS). Works for both dynamic and static data with full control over the color of each line in each frame. It has no dependencies and it is ideal for embedded systems with low resources or large datasets. For example, software-based oscilloscopes, Arduino, microcontrollers, FPGA user interfaces. This framework also can be used in combination with ElectronJS.

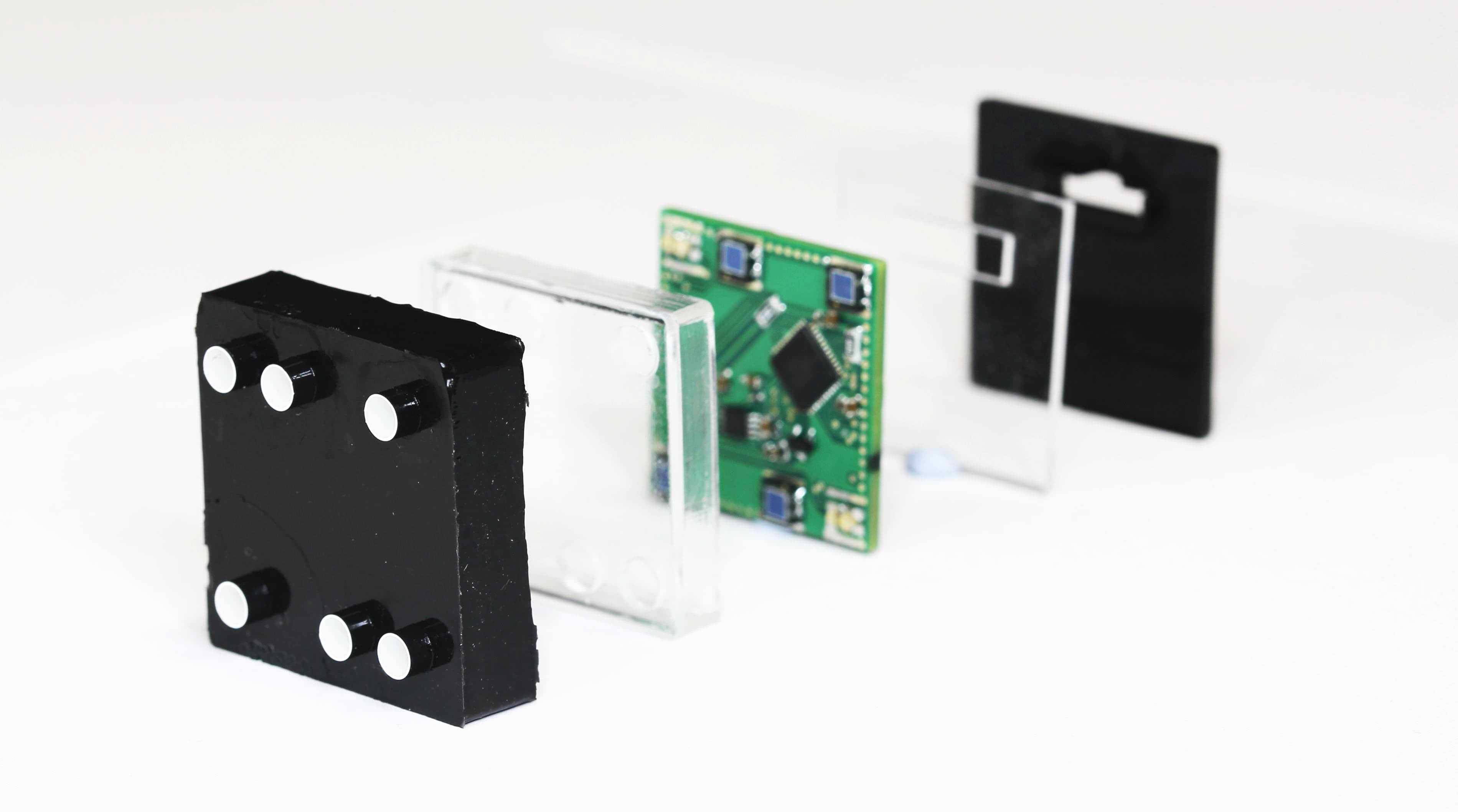

Developed for EPSRC (EP/K020315/1), this miniaturised near-infrared spectroscopy tile consists of 2 sources and 4 detectors in a 30x30 mm2 square shaped encapsulation. Each tile is part of an array of tiles which are easily connected to create an imaging array. The tile has silicone encapsulation for clinical use and benefits from novel soft silicone rods for better optical coupling and clearing hair. The optical sensitivity of the detector is approximately 370 fW which means measuring pico-amps of electrical current on the head.

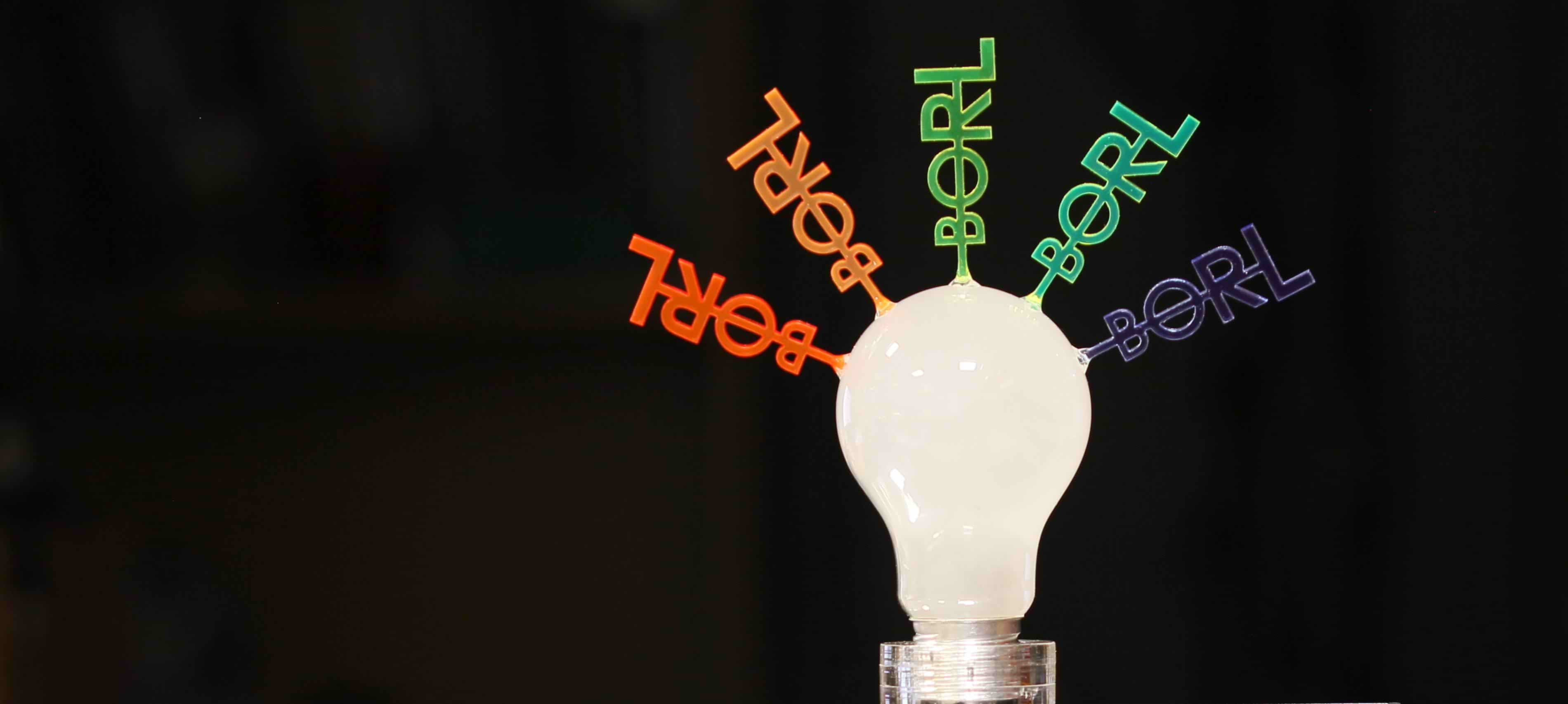

Originally created for the Wellcome OnLight exhibition (London, 2015), also later featured in the UCL Spark festival, it was part of the contribution of the UCL BORL group to these two public engagement events. The BORL bulb was a hollowed-out incandescent bulb filled with lightly scattering silicone and illuminated from below with a 40W RGB LED. Three large dials on the front of the enclosure adjusted the amount of blue, green and red colour intensities. Unlike most LEDs with focused illumination, the visitors experienced a unique visual of colour mixing due to the volumetric scattering occurring inside the bulb. Now, the bulb has a permanent home in the UCL Medical Physics museum.

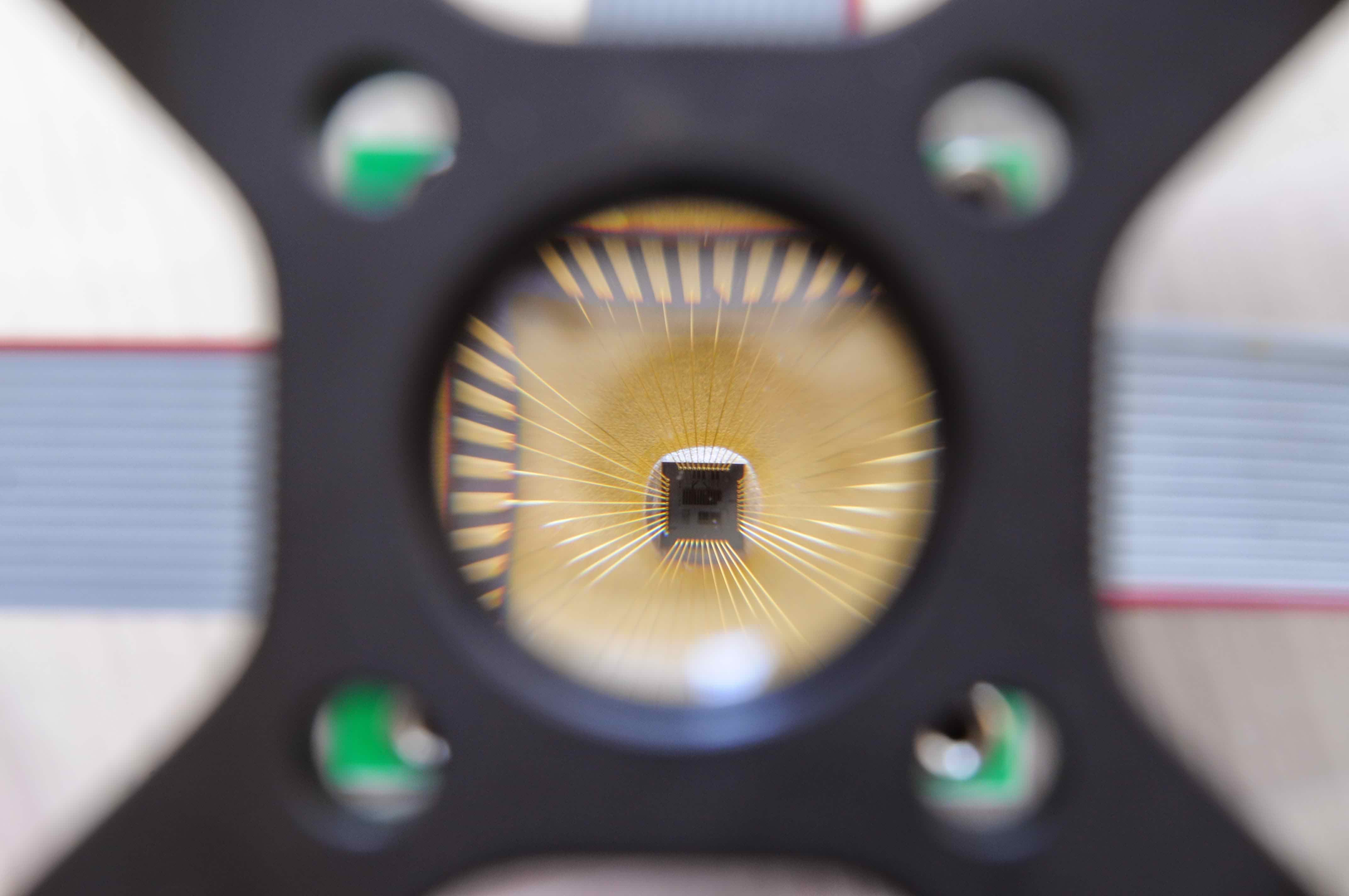

This multi-wavelength LED was developed as part of EPSRC (EP/K020315/1) project for Near Infrared Spectroscopy (NIRS). Conventional NIRS probes use 2 to 3 wavelengths in their sources. Additional wavelengths increase the accuracy of resolving multiple chromophores in the blood, however adding further wavelengths increases the size of source hence reduces the spatial accuracy of the measurement. As a result, a miniaturised multi-wavelength LED source was developed consisting of eight discrete wavelengths from 650nm to 950nm. The die attachment, wire-bonding, and encapsulation processes were performed in-house.

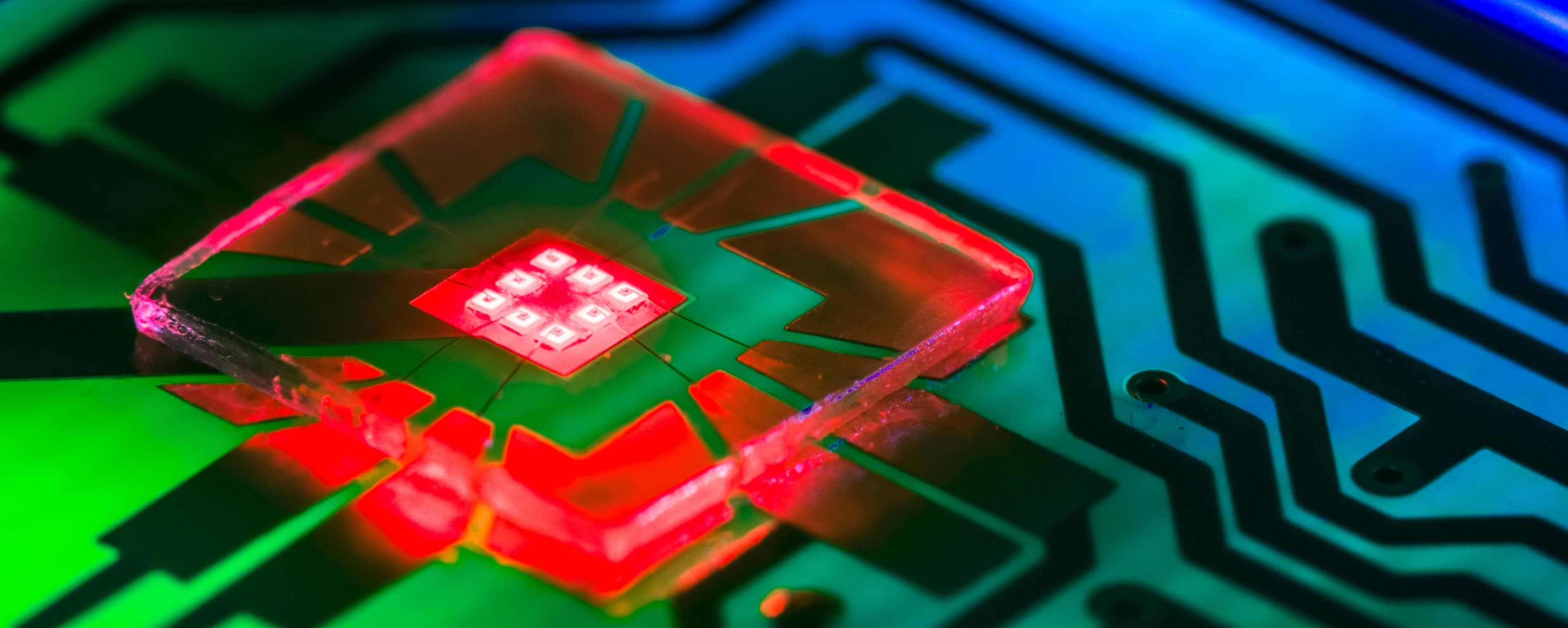

In later part of my doctorate at Oxford, for the first time, I utilised the integrated SPAD in free space optical communications. Using numerical simulations, I demonstrated that bit times faster than deadtime can be achieved with an array of SPADs. I implemented a array of 64 SPADs with a fast differential current driven analogue output. Speeds of up to 200 Mbps ON-OFF keying were achieved with a deadtime of 5ns. This proof-of-concept integrated circuit demonstrated that it is possible to use an array of SPADs instead of conventional APDs where integration is advantageous.

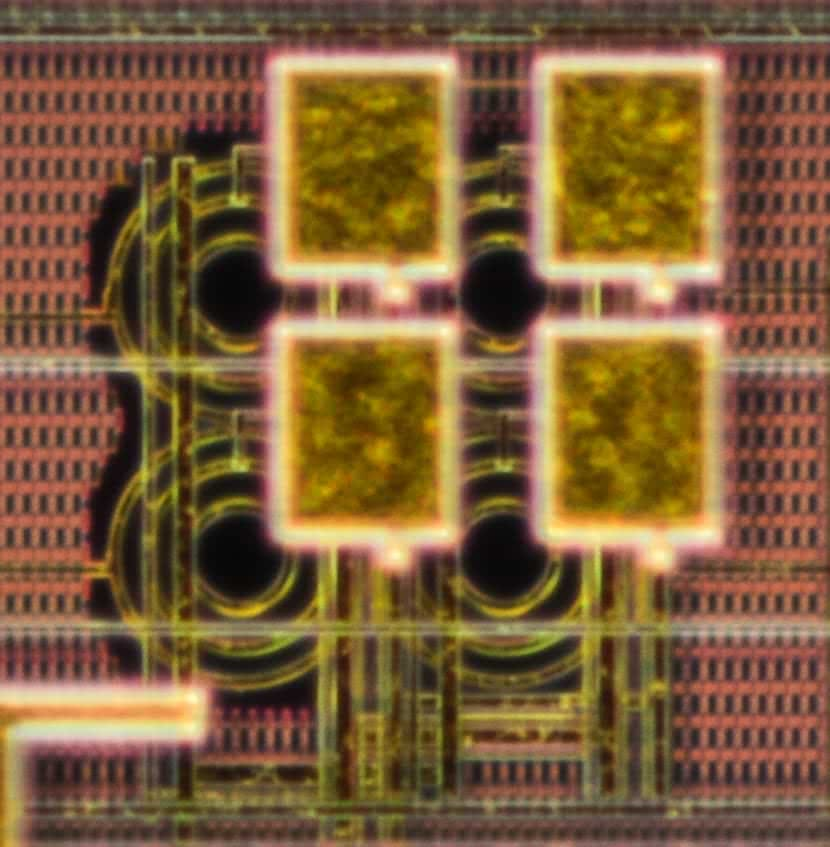

As early part of my doctorate studies at Oxford, I developed an analogue SPAD pixel which utilised the small gap between circular SPADs. The readout was compatible with conventional CMOS pixels. Digital SPAD pixels used a counter to store the number of detected photons. However, this counter occupied a large space relative to the diode. Instead the analogue pixel, stored the number of detected photons as a charge on the integrated metal capacitor which was placed above the quenching circuit. The stored charge was readout as an analogue voltage similar to CMOS pixel arrays.

Even after the introduction of digital cameras, for years, professional photographers have preferred to use film-based SLR cameras for their photography. The main reason for that was a lower pixel count in a digital camera image sensor compared to a film. Nowadays, with newer technologies in semiconductor fabrication, this problem has been overcome by many pixels in a smaller area. Image production workflow from capture to display has been made easy, quick and robust by electronic circuits. New imaging technology created new areas in photography. One of these areas is HDR (High Dynamic Range) photography.

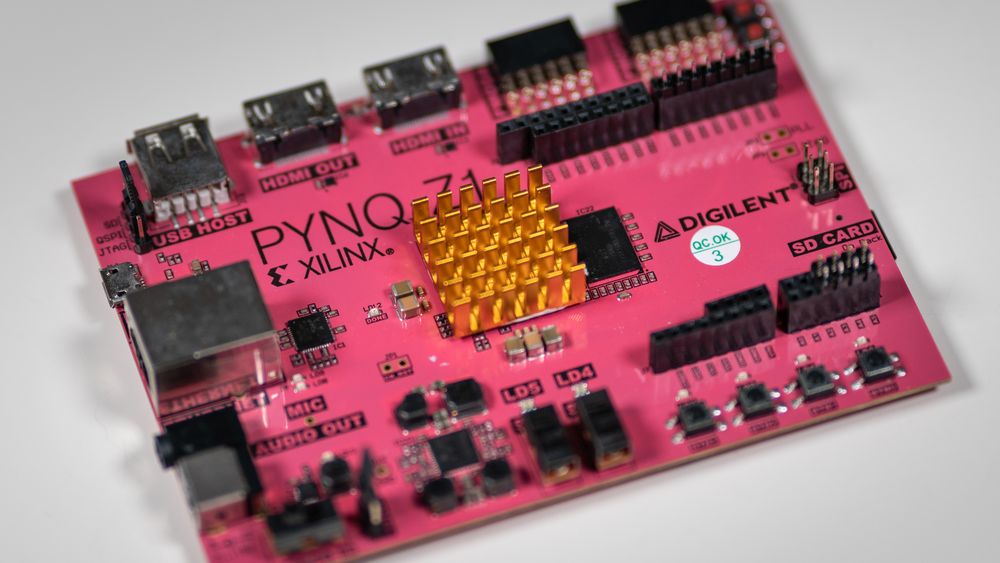

As part of my final BSc project, I opted for a digital design project with FPGAs and Verilog. During the undergraduate laboratories, I had built digital circuits using discrete AND / OR gates on breadboard. This was very cumbersome, and I was intrigued when introduced to the concept of FPGAs. My project was a real-time text overlay on PAL/NTSC video signals. This was useful for annotations and graphics for video broadcasting. I used Xilinx Spartan-3E coded in Verilog and few external components to complete this project.

In early 1998, I was inspired by “The Fractal Geometry of Nature” by Benoit Mandelbrot. I developed a series of software which plotted Iterated Functions system (IFS), Julia sets, and Borwnian motion (1/f) fractals. At the time I had updated my PC from a Philips 80286 (12.5 MHz) running DOS 4.1 to a Pentium 166 MHz running Windows 95. I wrote my code in the new programming language Java 1.1. It took overnight runs to generate A4 size 600dpi (2870 by 6250 pixels) images. However, unfortunately none of the codes runs today without a complete re-compiling due major changes that happened to Java applets. I have started to re-write these code in Matlab which will demonstrate the principles of Fractals.